前言(设计初衷)

由于自己笔记本插接口不多,在网上购买了一款USB扩展坞,但平时要往返宿舍和工位,书包要放课本、笔记本等,不想再增加重量就动手搞一个放工位上方便。自己动手,丰衣足食(哈哈哈哈其实是自己不想包里放太多东西,同时也想练练画板),接下来就开始进入我们的主题。

一、硬件方案

本设计采用第三代全集成单芯片USB3.0集线器控制器VL812作为USB3.0的主控芯片(可用VL813代替),其支持一个上游端口和四个下游端口的超高速传输,故将4个Type-A作为下行口用于输入设备接口端,将Type-C作为上行口用于与笔记本(主机)通讯及板子供电。但由于vl812缺乏处理Type-C接口所需的逻辑与引脚,故需要使用USB Type-C 2:4差分通道多路复用开关转换芯片VL160来桥接VL812和Type-C接口。

1、VL812

VL812是一款第三代全集成的单芯片USB 3.0集线器控制器,采用QFN-76L绿色封装(9x9x0.85 mm),适合小尺寸设计。

①强调低功耗设计,并集成了行业首个5V DC-DC开关稳压器;

②支持USB 3.0规范的高速传输,允许最大数据传输速率达到5Gbps,是USB 2.0的10倍;

③采用先进的CMOS工艺,其集成的内部USB PHY支持一个上游端口和四个下游端口的超高速传输,同时向后兼容以前的USB规格,提供支持高速(480Mbps)、全速(12Mbps)和低速(1.5Mbps)的流量。

其非常适合独立的USB集线器、桌面电脑前面板集线器、车载集线器、对接系统和包括鼠标、键盘、显示器和打印机USB设备的USB集线器复合设备。

2、VL160

VL160是一款USB Type-C数据开关芯片,采用QFN-28 3.5x4.5mm的绿色封装,它具备CC(Configuration Channel)功能,用于USB 3.1 Type-C应用。这款芯片主要用于USB与Type-C之间的数据传输,常见于扩展坞和Type-C转USB接口等产品中。

①支持4:2的USB Type-C数据开关,即它可以将四路差分信号复用为两路,或者将两路差分信号解复用为四路,以适应不同的应用场景;

②集成了内部电源开关,支持Vconn 5V供电,并具有过流保护功能;

③具有低功耗特性,有源状态下功耗为0.5mA,待机状态下仅为4uW;

④支持高达10Gbps的数据传输速率,兼容USB 3.1 Gen2标准,并且具有高直流共模电压支持,可达到2.2V;

⑤在ESD保护方面,VL160能够承受超过4KV的静电放电,CDM(接触放电模型)超过500V。

3、Type-C

USB Type-C接口是一种现代的连接标准,它以其可逆插拔设计、高速数据传输能力和高功率传输而受到广泛欢迎。24Pin Type-C接口共有24个引脚,包括4个VBUS电源引脚、4个GND接地引脚、2对USB 3.0差分信号线、2对USB 2.0差分信号线、2个CC(Configuration Channel)引脚用于设备识别和PD快充,以及2个SBU(Sideband Use)引脚用于特定传输模式下的辅助信号传输。其引脚功能定义如下:

①VBUS和GND引脚:提供电源和接地,共有4个VBUS和4个GND引脚,支持高达5A的电流。

②USB 3.0差分信号线:包括2对SuperSpeed差分信号,用于高速数据传输。

③USB 2.0差分信号线:包括2对USB 2.0差分信号,用于兼容旧版USB设备。

④CC引脚:用于设备识别和PD快充协议的通信。

⑤SBU引脚:在特定传输模式下使用,如DP(DisplayPort)功能开启时,用于传输设备的DPCD、EDID等关键信息。

4、Type-A

USB Type-A接口是一种非常普遍的USB接口形式,它被广泛用于连接计算机和各种外部设备。9pin Type-A接口是USB 3.0标准的一部分,它在传统的4针脚Type-A接口基础上增加了5个针脚,引脚分布如下:

VBUS(引脚1):电源线,提供+5V的电压,通常由红色线表示。

D-(引脚2):数据线负,用于USB 2.0数据传输;

D+(引脚3):数据线正,用于USB 2.0数据传输;

GND(引脚4):地线,用作信号的地线;

StdA_SSRX-(引脚5):高速数据差分对-接收负,用于USB 3.0高速数据接收;

StdA_SSRX+(引脚6):高速数据差分对-接收正,用于USB 3.0高速数据接收;

GND_DRAIN(引脚7):信号地,用于消除EMI干扰,保持信号完整性。

StdA_SSTX-(引脚8):高速数据差分对-发送负,用于USB 3.0高速数据发送;

StdA_SSTX+(引脚9):高速数据差分对-发送正,用于USB 3.0高速数据发送。

额外的针脚(5-9)使得USB 3.0能够提供高达5Gbps的数据传输速率,并且支持全双工通信,即数据可以同时双向传输。这种设计显著提高了数据传输效率,并且减少了传输延迟。9pin Type-A接口的物理设计也包括了对电磁干扰的屏蔽,以确保信号的完整性和设备的兼容性。

二、原理图设计

关于原理图的设计,需要查看元器件的数据手册,以VL812为例,先看Product Features了解该芯片大致功能,是否符合项目所需,其次看引脚定义Pin Descriptions了解引脚功能,有的数据手册会给出芯片原理图示例,也需要进行参考等,以及引脚相应的电气特性(注:每个芯片需要关注的信息并不完全相同)

1、VL812模块

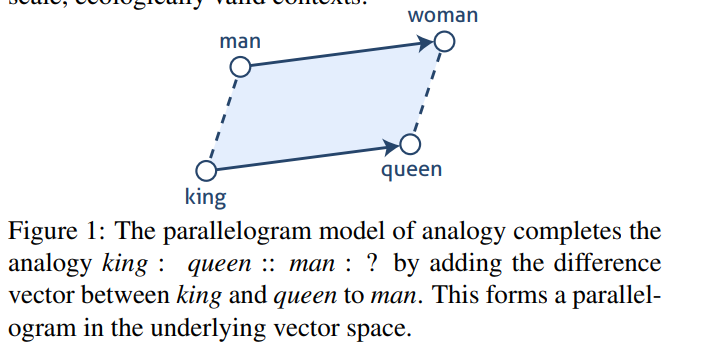

从上图原理图的设计,我们通过数据手册进行解释:

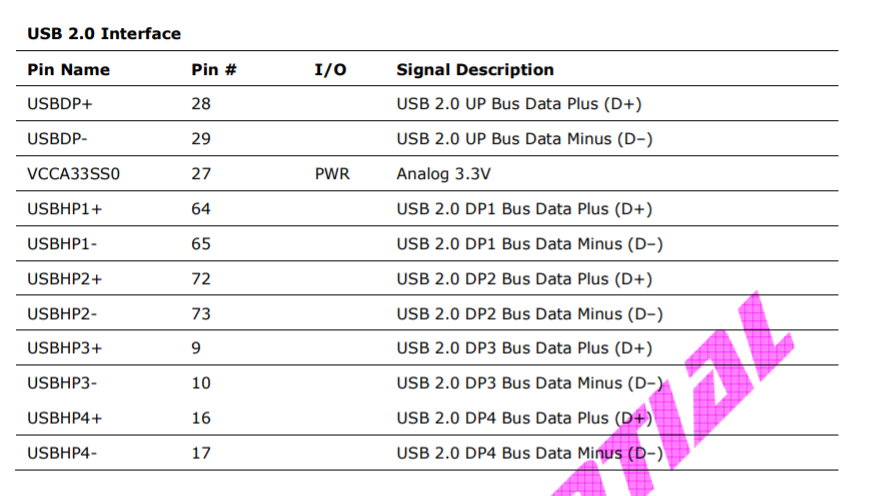

①对USB2.0接口进行导线引出,并使用网络进行命名,其USB2.0引脚名称可从数据手册得知,如下图所示(熟悉后不看数据手册也能清楚USB2.0为哪些引脚):

从而在原理图上进行命名为:HP1,HP2,HP3,HP4,DP,3V3.

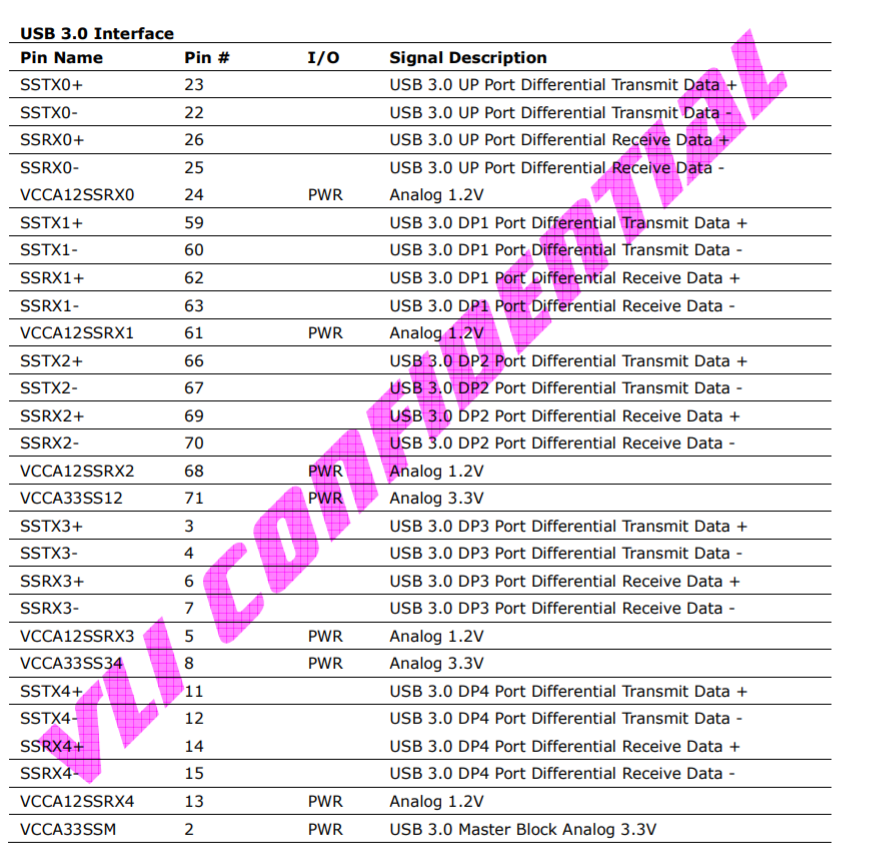

②同理,观察USB3.0接口数据手册进行命名,如图所示:

③对于数据手册上该信息:

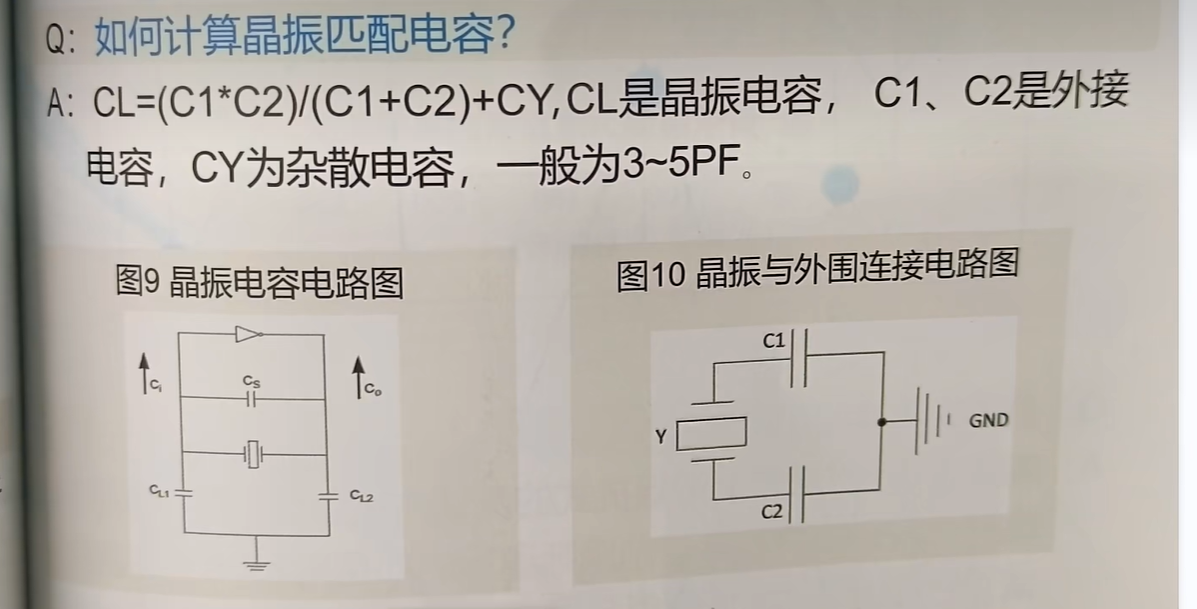

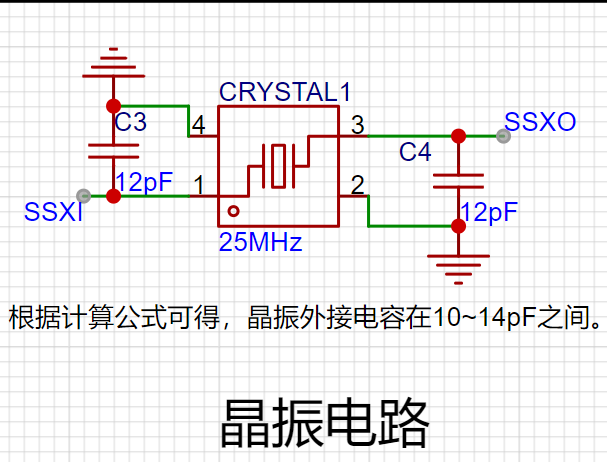

可知SSREXT需要连接电阻以进入高速模式,这里由官方可知外界电阻应为6.04KΩ。SSXI,SSXO需要连接25M晶振,而晶振电路都需要匹配电容,这里给出晶振匹配电容计算方法:

首先,选择的晶振它的晶振电容为10pF,由公式可知,CL=10PF,CY位于3PF-5PF之间,假设C1=C2,可求得C1=C2=10~14PF,这里居中选取C1=C2=12PF。

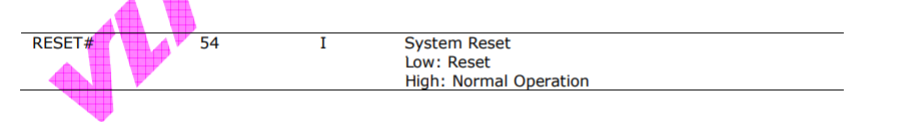

④对于RESET#为系统复位引脚,

由数据手册可知当其为低时复位,高时为正常运行,故设计以下复位电路图:

原理分析:上电瞬间,由于电容两端不会发生突变,此时RST低电位,系统复位,随着3.3V通过RC电路对电容充电,待电容两端电压达3.3V时RST为高电平,此时系统工作。

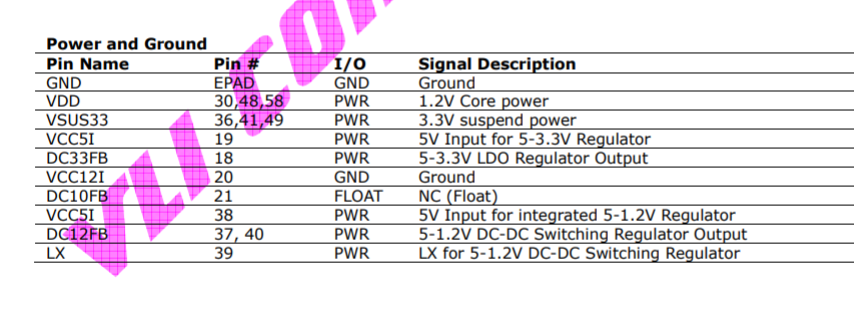

⑤接下来看到数据手册Power and Ground信息:

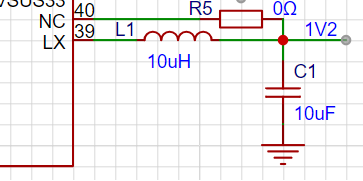

对于其中的GND,VDD,VSUS33,VCC5I,DC33FB,VCC12I,DC10FB,VCC5I,DC12FB引脚仅需通过读其Signal Description就可进行网络命名,而对于LX引脚,它是用于5-1.2V的DC-DC开关转换器,由

官方案例可知,需要加一个10uH的功率电感和一个10uF的电容配合内部的DC-DC芯片工作,1.2V的电源最好是经过10uF的电容之后再流出给其他引脚。(注:电感选择时考虑体积,电流尽量不要小于1A,流出余量,10UF的作用是用来滤波)这里,可观察到40引脚在原理图是NC标志,这里使用0R进行连接引出1.2V,这是为了后续这个引脚有用的话仅需焊接0R电阻上去即可。

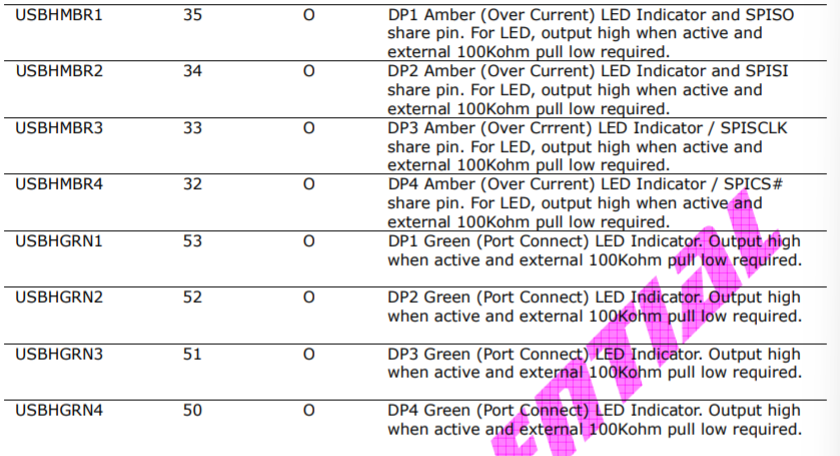

⑥接下来看到USBHMBR 和 USBHGRN 这8个引脚,数据手册是这么描述的:

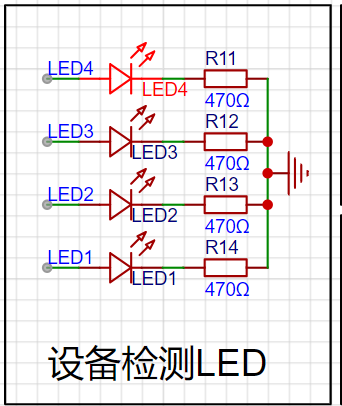

首先可以知道这8个引脚接LED,其中USBHMBR 4引脚是过电流时LED指示(可用于警告用户存在潜在的电源问题或设备故障),USBHGRN 4引脚是下行端口处于活动状态时LED指示,由于这里暂时不需要提示过电流状态,因此USBHMBR引脚采用非连接,而USBHGRN采用连接LED,通过外接10K电阻拉低。

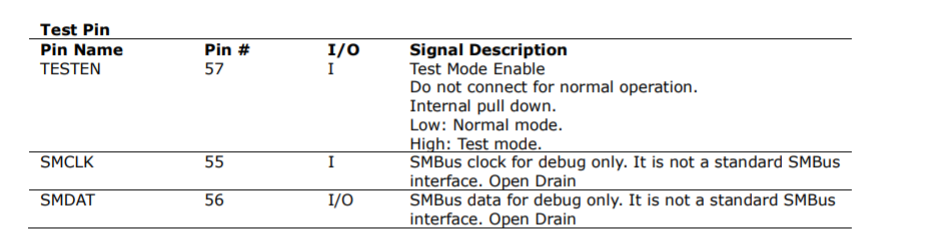

⑦然后看到Test Pin,由数据手册可知:

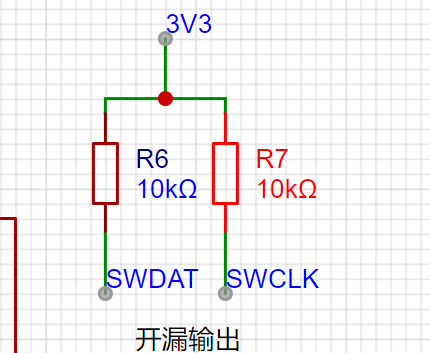

57引脚应接地处于正常模式,55,56引脚仅用于debug模式,采用开漏输出,故需要外接10k电阻到3.3V.

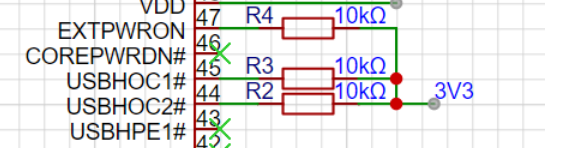

⑧通过数据手册,可知:USBHPE2B#引脚为USB充电接口,USBHPE1#为进入gang模式的端口电源(代表将四组输出端口作为一组绑定,通过检测电流之和进行报警,这里并没有使用过电流检测功能),COREPWEDN#引脚为核心断电(用于控制外部核心电源开关)(这里采用的是内部的核心故不能断电,又其为O(输出)),故以上三个引脚无需控制。

⑨对于USBHOC1,USBHOC2为过电流探测,当为低电平时端口过流,为高电平时正常供电,故这里采用高电平;而EXTPWRON引脚为上行端口检测,这里先采用接10K电阻进行上拉,即三个引脚都外接10k电阻上拉到3.3V.

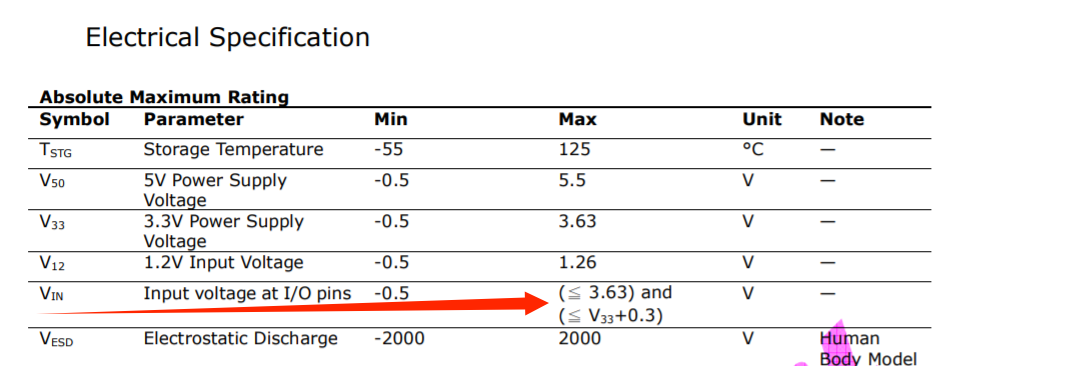

⑩VBUSDET引脚在数据手册上表示为USB 5V是否存在检测,根据官方示例,当引脚为高电平时存在5V输入,引脚低电平时不存在5V输入。此时,可观察到Vin输入电压最大值应 <= 3.63V

因此不能直接拉到5V,而是位于3.3V左右,这里需要通过两个电阻进行分压,原理图设计如下:

至此,VL812芯片原理图部分设计完毕。

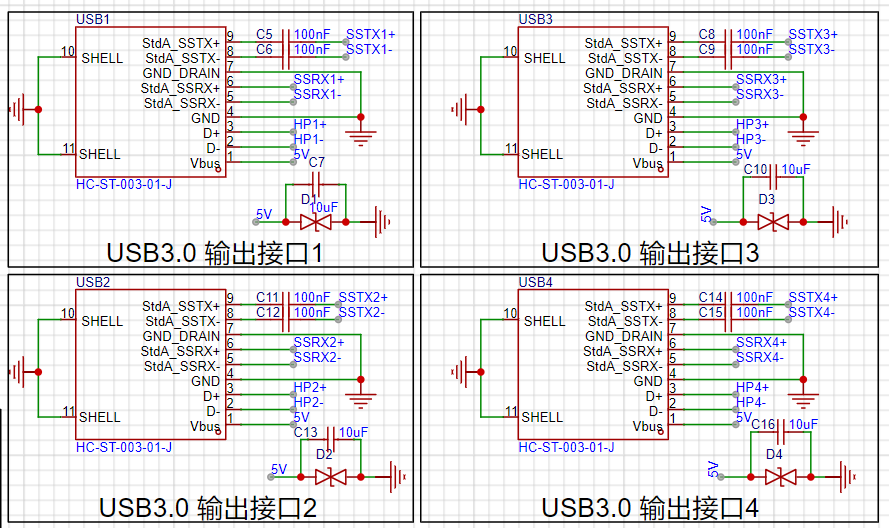

2、下行端口模块

采用4个Type-A作为其下行端口,在其SSTX处串联100nF电容减少低频干扰,提升信号质量,同时在接口输入电源处放置10uF电容进行滤波,以及添加一个TVS(瞬态抑制二极管)防止浪涌和静电,在进行选型时需选择反向截止电压大于等于5V(正常工作时是5V状态,此时TVS不工作,漏电流小)

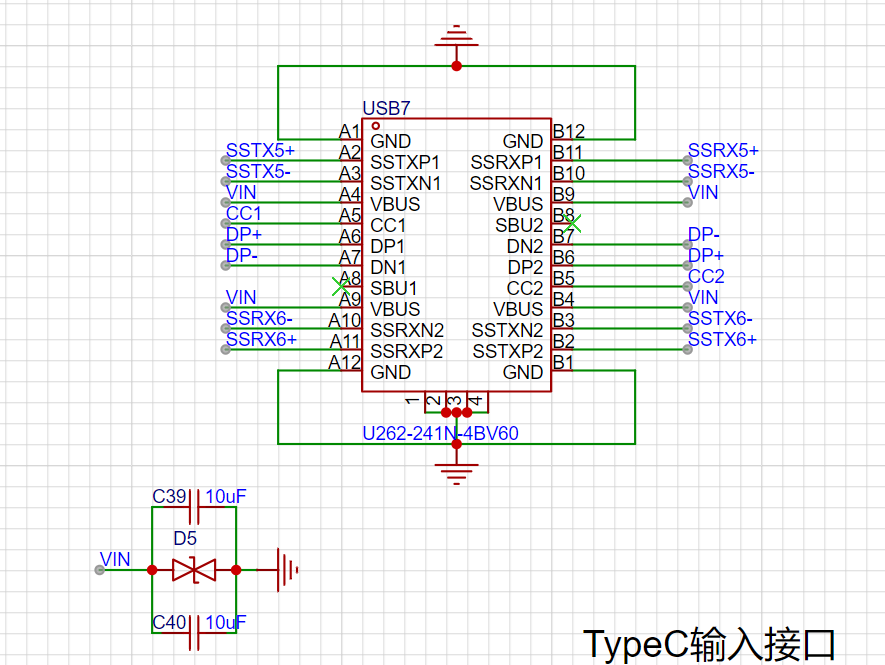

3、上行端口模块

同理,由2可知,Type-C作为上行端口原理图设计如下:

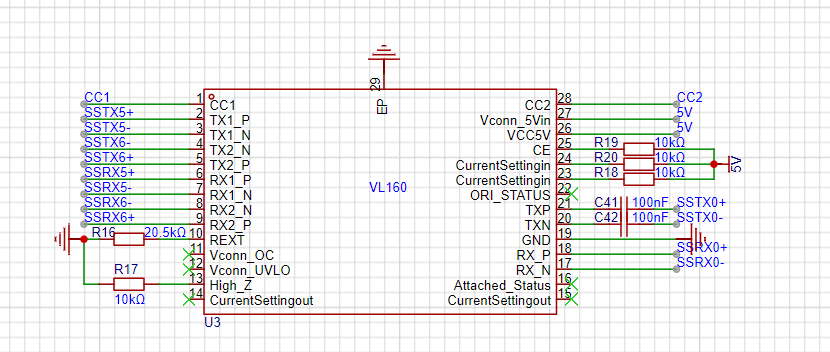

4、VL160模块

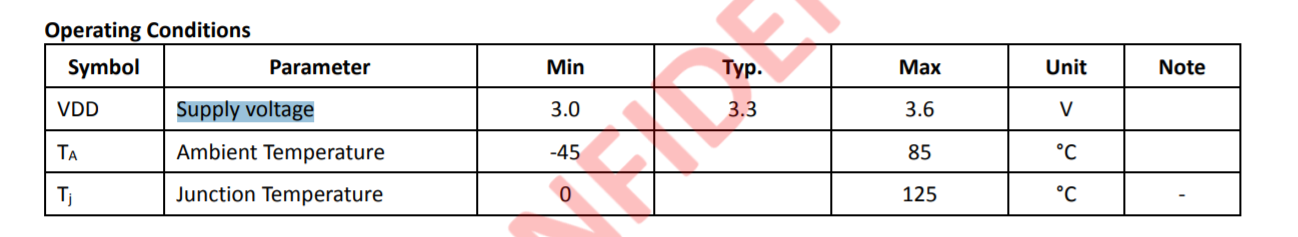

VL160在这里用于将Type-C转USB3.0,通过阅读数据手册可知,

(注:VL160在手册中电气特性要求供电电压在3.0~3.6之间,但由于VL812需要5V输入,因此这里采用5V供电,从网上结果来看该芯片可支持5V供电,并具有过流保护功能,意味着理论上可使用5V输入,但为了保证芯片稳定性和安全性,建议按照芯片数据手册设计)

①TX_P,TX_N,RX_P,RX_N分别接Type-C的两对差分信号线;

②REXT需外接20.5k电阻连接到GND;

③High_Z引脚是用于关闭CC1/CC2上的Rp/Rd,这里并不需要因此采用正常模式,通过10K电阻接地;

④CurrentSettingin两引脚,(以下个人理解,如果有不对处请指正),由数据手册及开头的分析,这里采用5V输入,根据比例计算可得出此时Rd为7.8左右,这里用10k来代替);而对于CE引脚,这是一个芯片5V使能引脚,故需连接5V电压;

⑤同理,TX引脚处串联100nF电容减少低频干扰,提升信号质量;

⑥对于Vconn_OC、Vconn_UVLO、CurrentSettingout这四个引脚,前两个分别表示过电流、欠电压状态,后引脚表示指示USB Type-C接口的电流设置,这里不需要不做处理;

⑦其余引脚只需引出网络名即可。

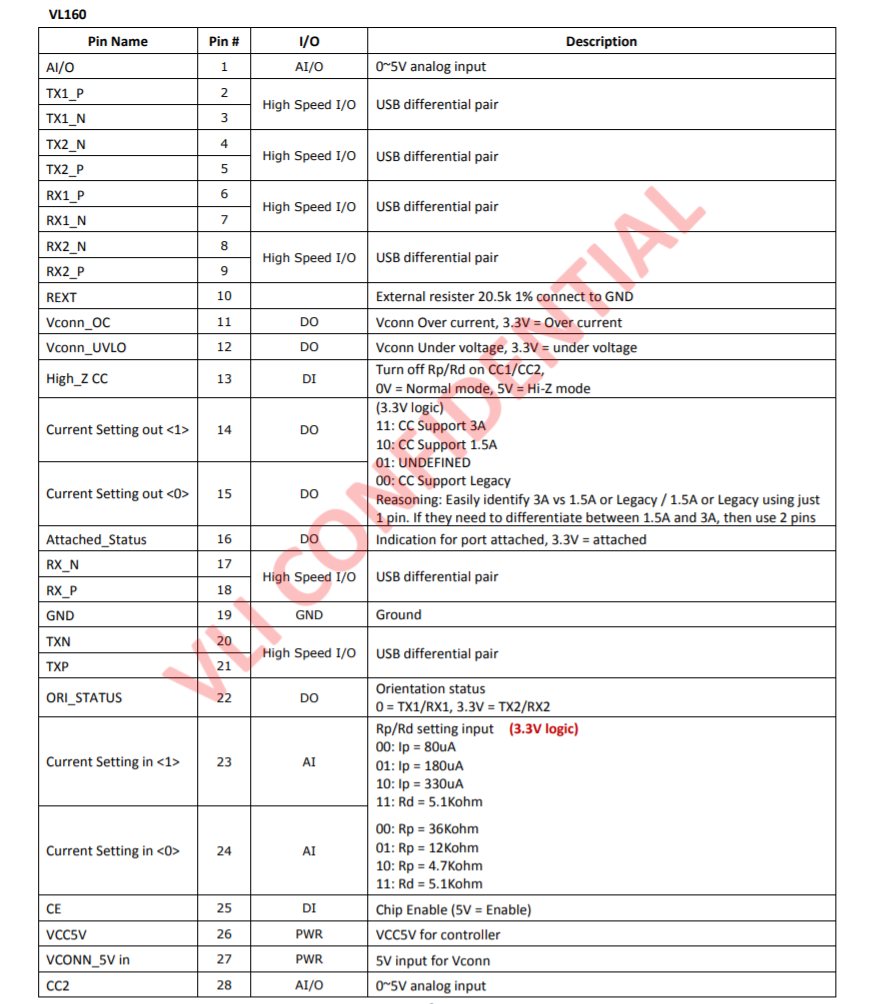

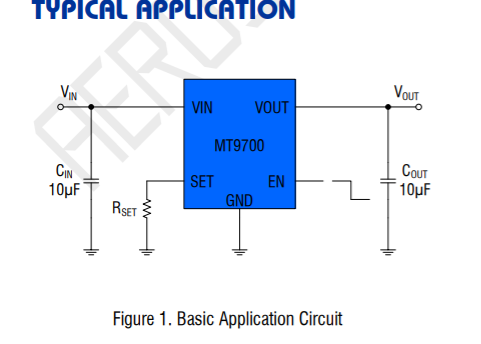

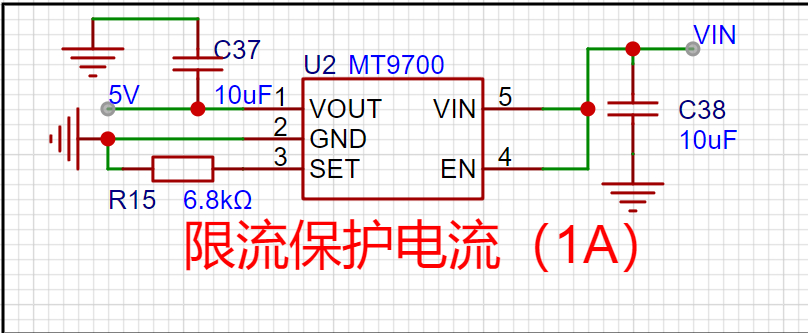

5、MT9700模块

一般笔记本接口输出电流在1A多,当四个输入接口所接负载比较大,就可能将电脑接口损坏,因此就需要一个限流保护芯片。这里跨过对其芯片的相关特征描述,直接看到数据手册上的典型应用:

一般情况,照典型电路进行设计即可,有时候也需要因情况修改,这里直接使用其典型电路设计。对于其中的Rset电阻,由电气特性可知,选用6.8K电阻。

最终设计的原理图如下:

至此,原理图部分便全部设计完成,接下来就进入PCB设计部分。

二、PCB设计

平时使用的是2层板,但对于USB3.0需要走高速线,要求更好的抗干扰,这里考虑使用四层板设计。

1、四层板

①默认情况下,四层板的顶层和底层的铜厚为1盎司,用于走关键信号线或者大电流的信号线。

②内层1和内层2铜厚为0.5盎司,一般在内层进行GND铺铜和走电流相对较小的电源线和信号线。

③一般会将其中一个层设置为接地层,不走其他的线,这样就会有一个完整的地平面,可以更好的抗干扰,同时方便进行阻抗匹配。

2、层叠结构

四层板常用的有两种结构,一种是顶层——GND层——电源层——底层;一种是顶层——电源层——GND层——底层。

选择时,通常这样考虑:

①如果器件都在顶层布局或布局较多,或关键信号线在顶层走线的话,接地层最好放在第二层,然后第三层设置为电源层,底层走其余的线;

②如果器件在底层布局较多,或关键信号线在底层走线连接的话,接地层最好放置在第三层,保证关键信号线的质量减少干扰。

本设计采用第一种层叠结构。

3、阻抗匹配

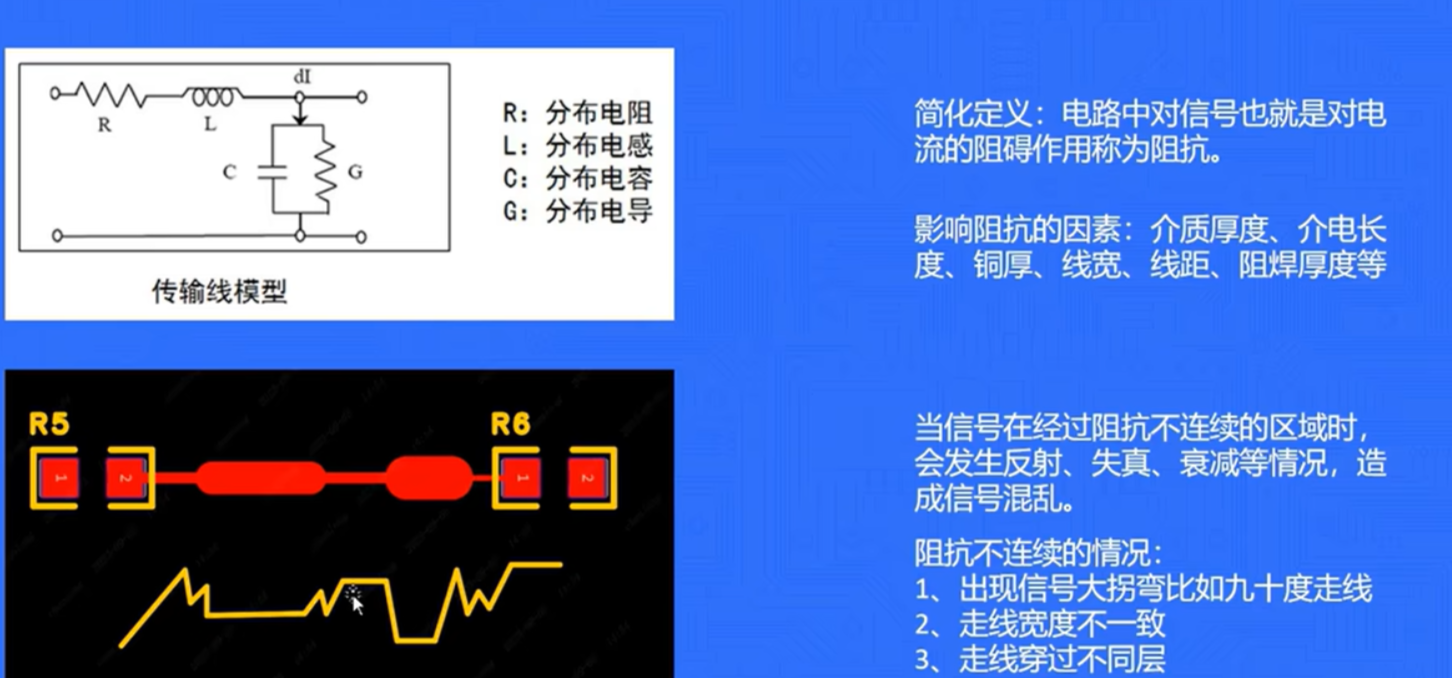

①定义:阻抗并不是单纯的电阻,平时使用的器件为非理想器件,会存在寄生电容,寄生电感,寄生电阻等会对电流起阻碍作用;(简单讲,就是在电路中对信号即对电流有阻碍作用成为阻抗)

②影响因素:介质厚度,介电长度,铜厚,线宽,线距,阻焊厚度等;

当信号经过阻抗不连续区域时,会发生信号反射、失真、衰减等情况,造成信号混乱。对于高速信号而言,这些情况很可能造成时序错误,从而导致通讯失败,比如两条或多条需要共同工作的信号线,如果传输信号速度很快,同时传输线之间阻抗差距比较大,一条线阻碍比较小,信号完整平稳地通过一条线阻碍比较大,信号存在较大的抖动,这就会导致信号混乱,时序错误。

所以在高速传输信号中,一般都会进行阻抗匹配,保证一组信号传输的一致性。

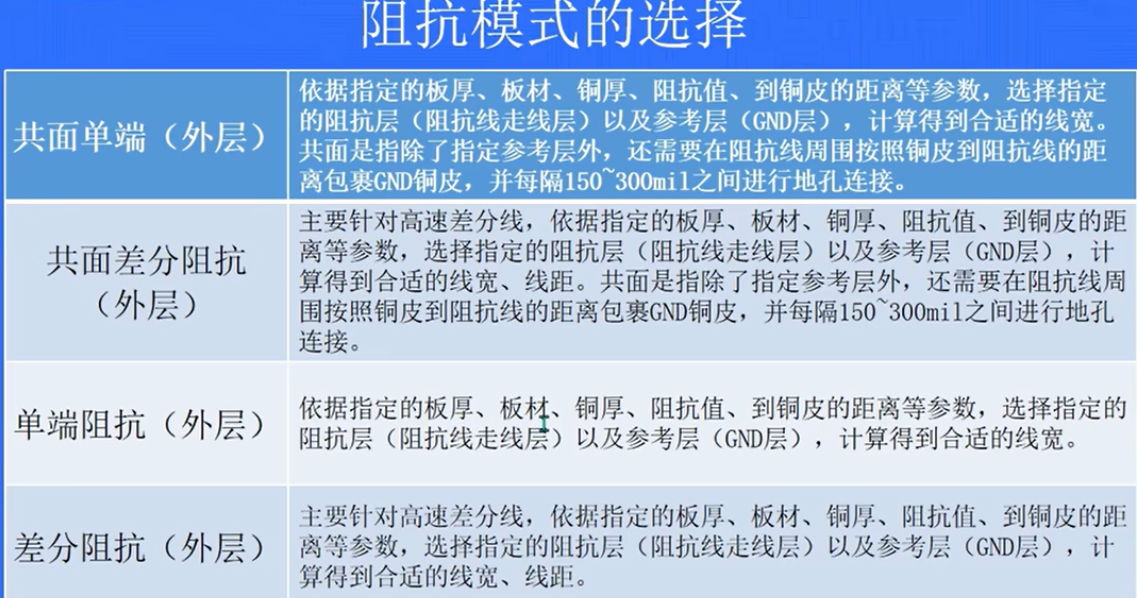

4、阻抗模式

一般有四种:共面单端(外层)、共面差分阻抗(外层)、单端阻抗(外层)、差分阻抗(外层)。那么,如何选择呢?

首先涉及高速信号线要差分处理,故第一点就是差分阻抗,那接下来考虑是单端阻抗还是共面阻抗:共面阻抗的抗干扰能力会更好,且PCB顶层基本为USB3.0所需元器件,故可考虑150-300Mil进行包裹。综上,使用共勉阻抗模式。

本设计中,我们可通过查询得知USB3.0Hub通常阻抗为90Ω,接着进入立创官网使用阻抗计算器计算导线线宽等,如下图所示:

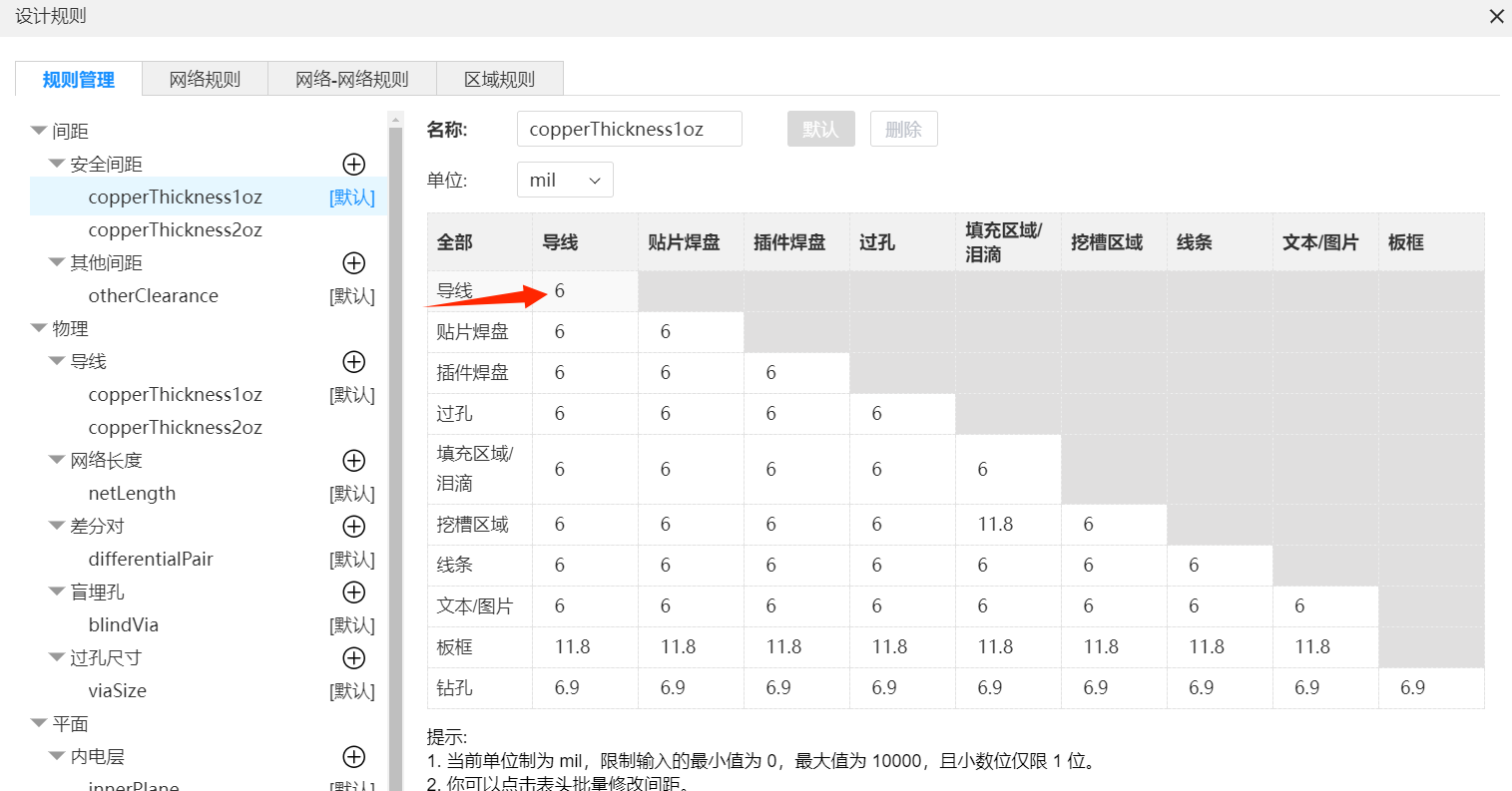

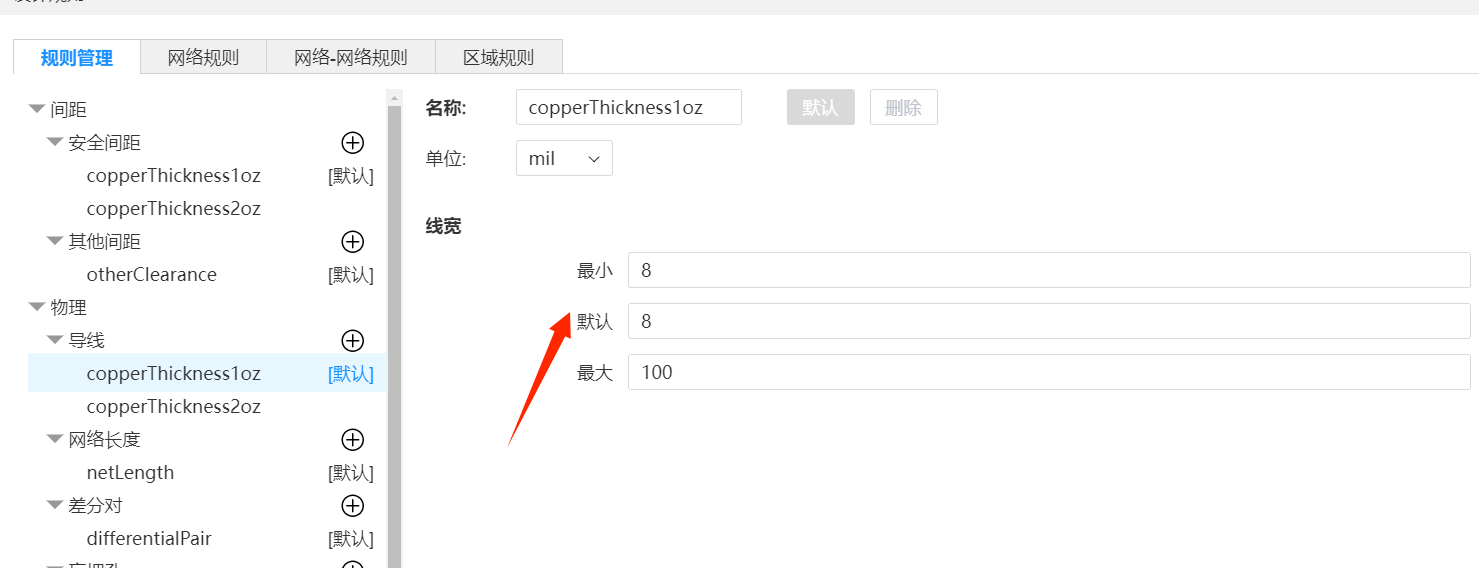

这里嘉立创能制定的PCB板一般不建议低于6mil,因此线距和阻抗线到铜距离设置为6min,通过计算得出线宽为8.38min,经过取整设为8mil.

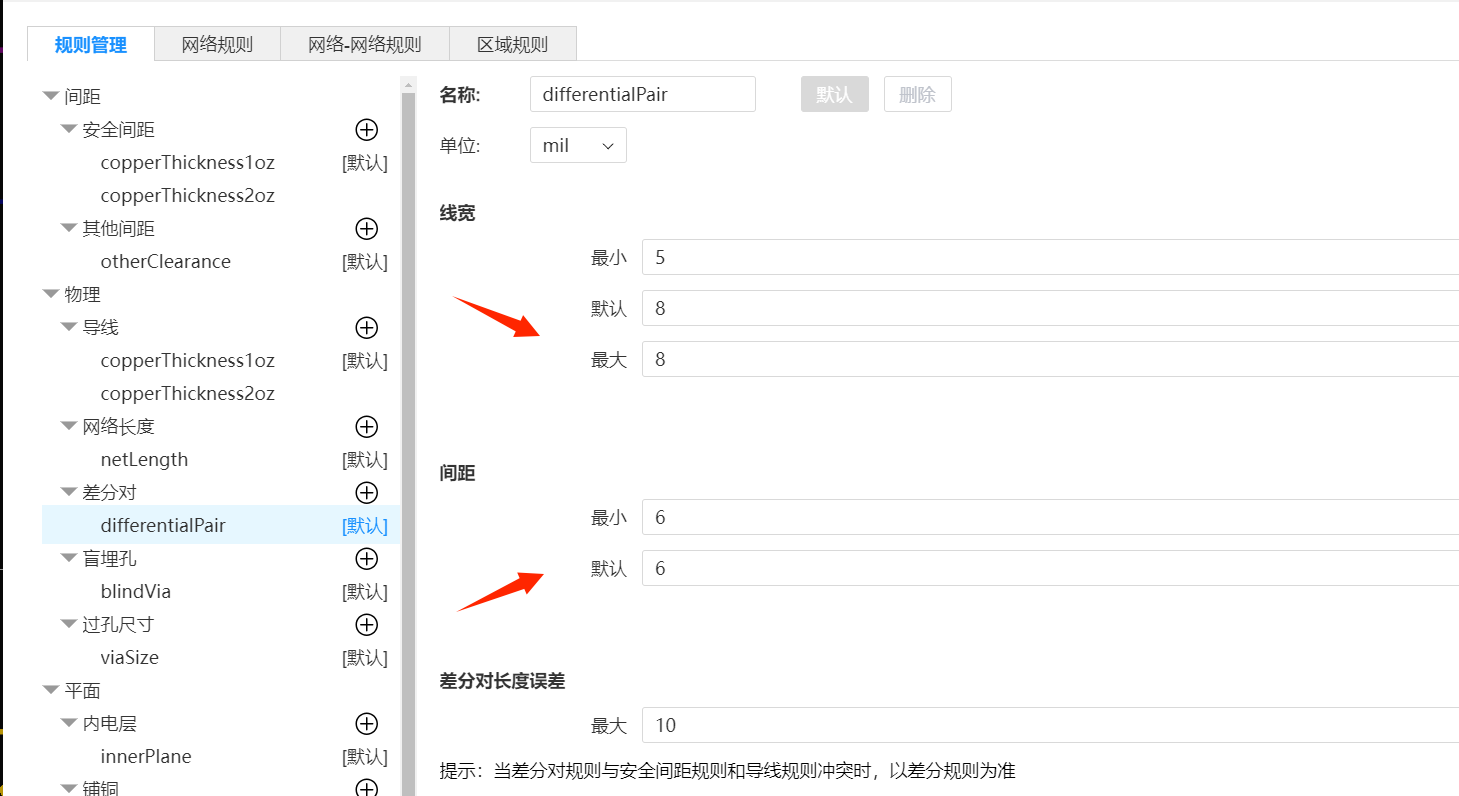

5、设计规则

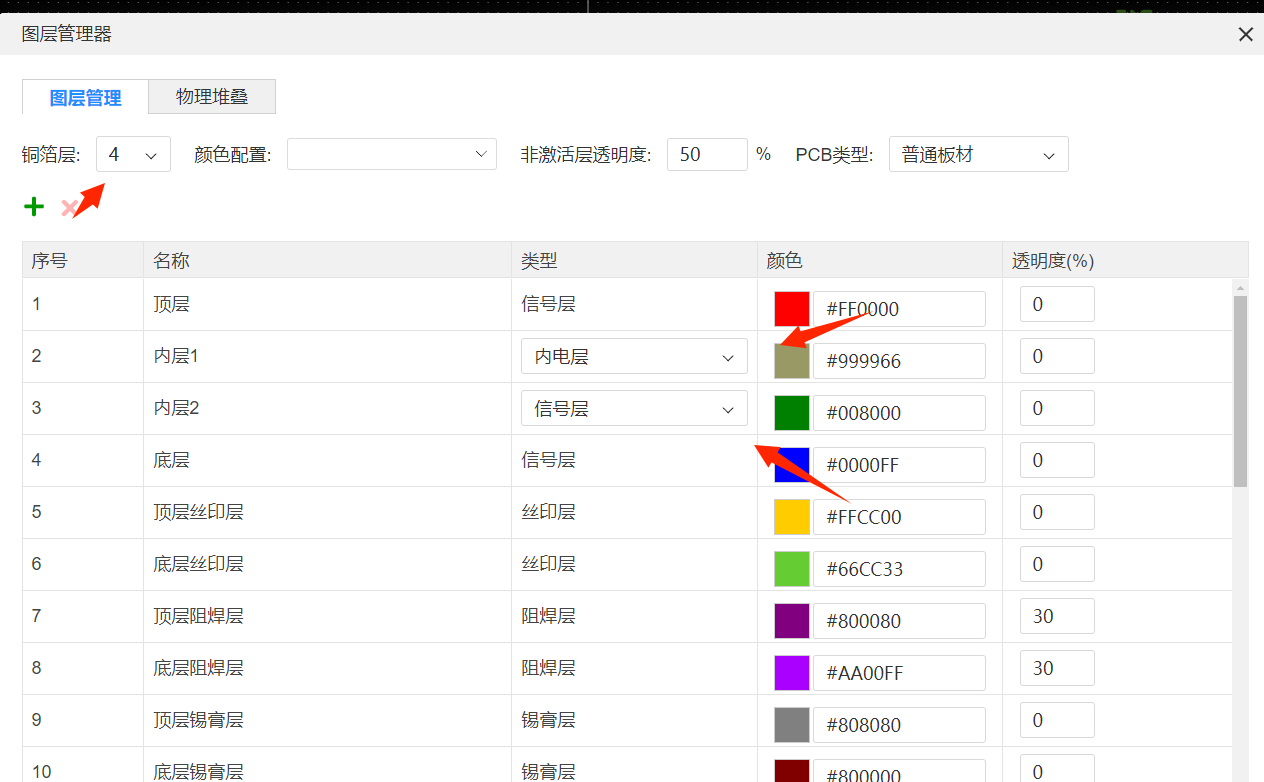

6、图层管理

将元器件摆放后,进入图层管理器,修改为4层板,并将内层2设置为信号层,用来走电源线。

7、差分对布线

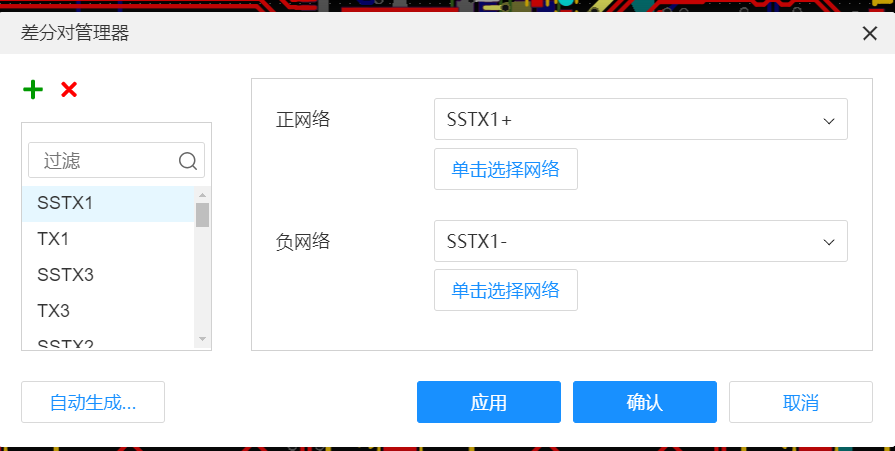

上方工具栏:设计——差分对管理器——一一设置差分线,如下图所示:

8、等长布线

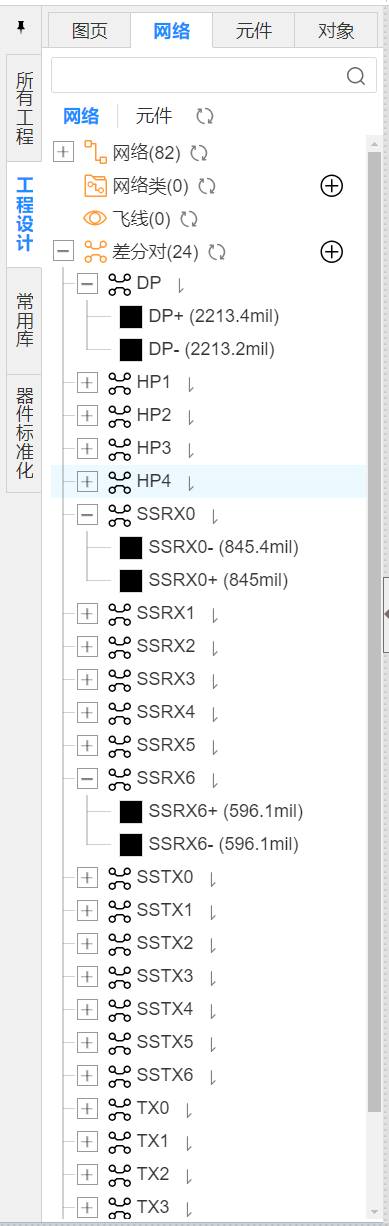

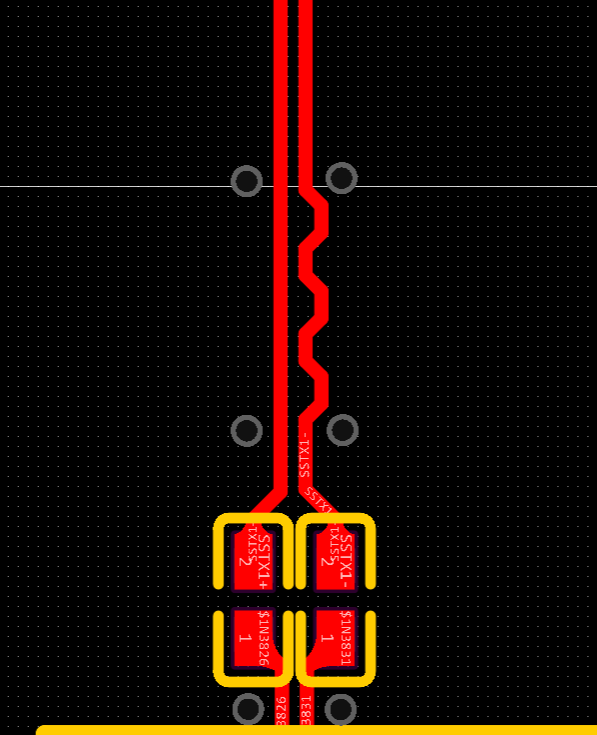

在PCB布局和布线完成后,需对差分信号线进行等长布线,在工程设计——网络——差分对中查看其差分信号长度,

对于差距大的,一般对于3.0信号线要在0.5mil误差内合适,2.0信号保持5mil内即可(当然越低越好),通过设计——等长调节(或直接shift+A),此时需要shift+A——Tab进行线差距设计,如下:

接下来就可以开始等长调节,这里给出示例:

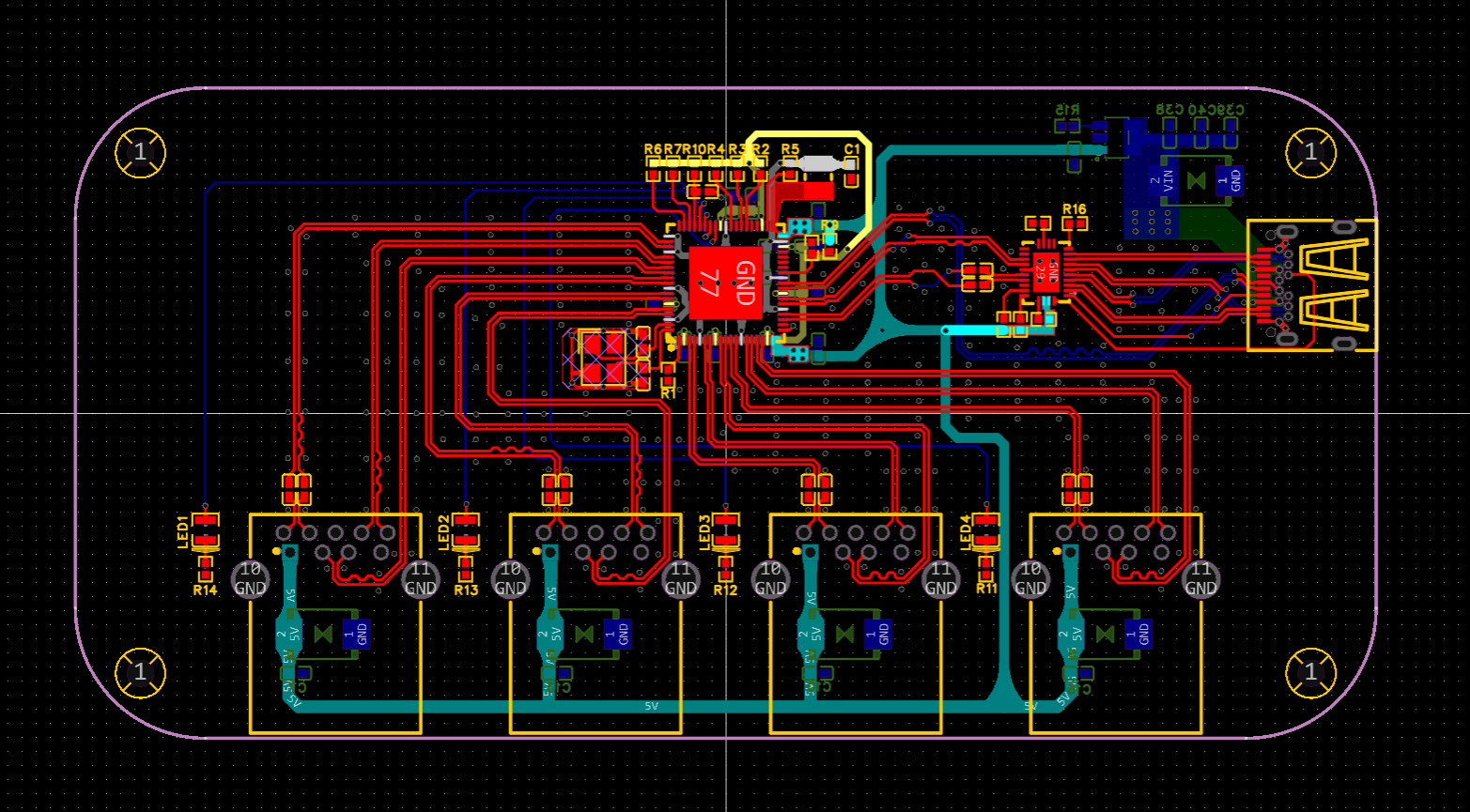

8、PCB图

以下是绘制后的PCB图,由于是昨天才绘制好,目前正在打板中,还未进行测试,后续等板子和元器件到了会进行焊接与测试(大概要下周三、四板子和元器件才到吧),大家有想法的话,等测试结束会把对应的原理图、PCB文件发在随笔末尾,供大家参考,若有不对之处请大家指出,一起学习、一起进步哈哈哈!

附:这里有几点说下:

①今天写了随笔才发现,在进行共面包地时,有几个GND网络没有严格按照GND相隔距离150-300mil进行放置,可能会导致稍许阻抗不连续,从而影响信号的传输质量。嗯,一切以后续测试结果为主;

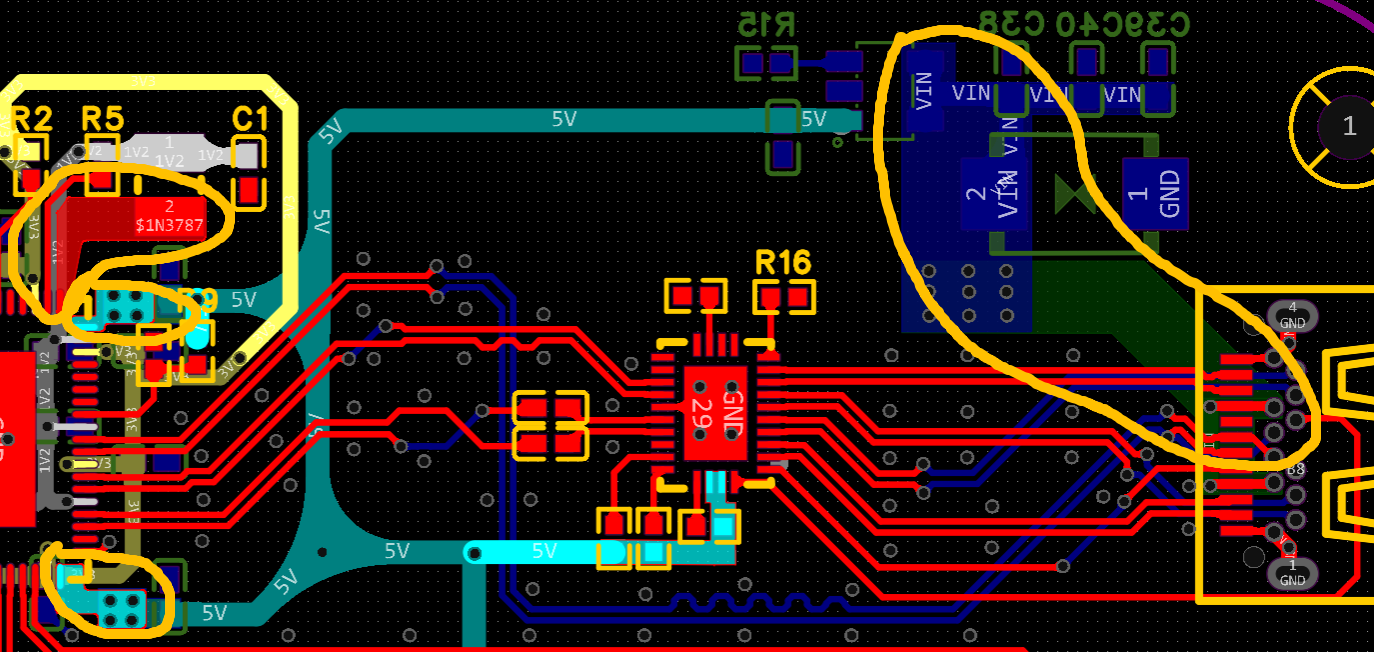

②对于以下三个地方,采用了多边形区域填充,为什么这么做呢?

通过区域填充,可以使得走过的电流比单纯导线走过的电流要大得多,同时采用过孔+区域填充可尽可能地保证5V输入的稳定(放置过孔时尽量分开,防止分割底下铜皮)。